## STREAMING EXTENSION OF GEN2 COMMUNICATION PROTOCOL

VER. 2.1, MAY 8, 2023 BACKSCATTER COMMUNICATION RESEARCH CONSORTIUM KEIO UNIVERSITY

### **1** Overview

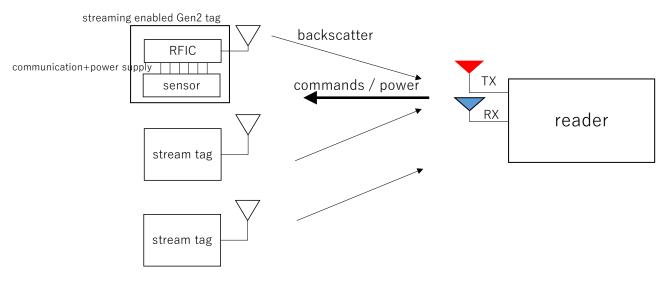

This document proposes an extension of ISO/IEC 18000-63 (2015) specification (hereafter referred to as Gen2)[1] or a new stream of protocol to enable concurrent sensor data streaming from multiple radio frequency (RF) tags with multiple subcarrier channels. The Gen2 streaming system comprises a reader/writer and a single or a group of streaming enabled Gen2 tags (hereafter referred to as reader and stream tags, respectively), as shown in Figure 1.

Figure 1 Streaming Gen2 system composition

As shown in Figure 1, a stream tag comprises an RF integrated circuit (RFIC) and a sensor connected to RFIC through, for example, the serial peripheral interface (SPI). The RFIC handles the communication with the reader using an extended Gen2 protocol. Additionally, it provides power to the sensor.

The Miller encoded subcarrier is extensively used in commercial Gen2 RFID systems. However, only one tag responds to its reader at a time. In the Gen2 streaming system, each stream tag in the view field of the reader is assigned a dedicated subcarrier channel by the reader, and the sensor data can be concurrently streamed using the subcarriers. An overview of the communication protocol is explained in the next subsection.

## 1.1 Communication protocol

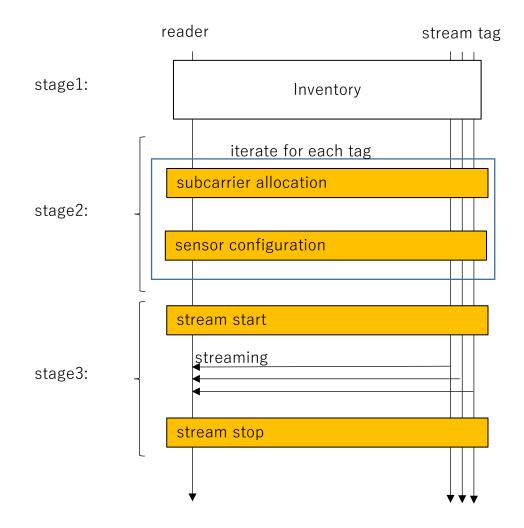

The high-level overview of the communication protocol is shown in Figure 2. The communication between the reader and stream tags progresses via the following three stages:

## Figure 2 Communication protocol between the reader and stream tags. Shaded blocks represent an additional protocol for Gen2

Stage 1 Inventory: During this stage, the reader inventories each of both the stream tags and standard Gen2 tags using Gen2 SELECT, QUERY, and related commands. Although the algorithm for subsequent subcarrier allocation depends on the reader's implementation, collection of received signal strength indicator (RSSI) during the inventory process is recommended. The practice adopted in this document is to assign the weak RSSI subcarrier to subcarriers close to powering continuous waves [3]. This is done to reduce mutual interference caused by subcarrier harmonics.

■ Stage 2 Subcarrier assignment and allocation: A unique subcarrier is assigned<sup>1</sup> and allocated to each stream tag using Gen2 WRITE command to specific memory addresses. Each stream tag is given a zone ID that distinguishes between the streaming zones. When the subcarrier is allocated, each stream tag is placed into the DCO\_LOCKED state, essentially awaiting the STREAM\_START command.

After the subcarrier allocation, the sensor in a stream tag can be configured using an RFIC-sensor interface such as SPI.

Stage 3 Streaming: To start streaming from all stream sensors, the reader sends a STREAM\_START command, which is chosen from one of the Gen2 RFU commands. Optionally, a STREAM\_STOP command can be used to stop the streaming from the stream tags with a specified zone ID.

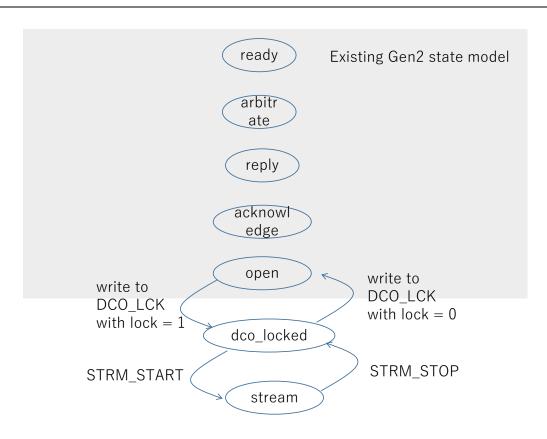

Each stream tag should be capable of inventory, read, and write operations in the existing Gen2. In addition to the present communication protocol, the stream tag should be capable of handling subsequent subcarrier channel allocation and data streaming, as shown in Figure 3.

<sup>&</sup>lt;sup>1</sup> Assignment means the determination of subcarrier frequency chosen for a particular stream tag. Whereas, allocation means the communication between the reader and stream tag that enables the stream tag to set the assigned subcarrier.

Figure 3 State transition of a stream tag

## 2 Communication protocol detail

#### 2.1 Subcarrier frequency and symbol definition

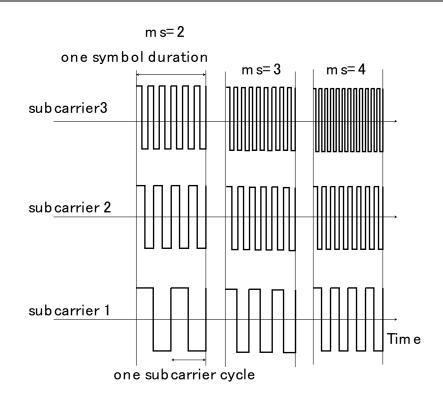

In Stage 3 of communication, one encoded symbol should be represented with at least two cycles of subcarrier. If a symbol is represented with only one cycle of subcarrier, it is baseband coding. The subcarrier frequencies in the stream Gen2 system comprise integer multiples of the base subcarrier frequency, as shown in Figure 4. In the figure, three base subcarrier frequencies are denoted by subcarrier 1 with  $m_s = 1$ , 2, 3. Notably, this coding is applied only to Stage 3; the standardized Gen2 coding and modulation specified by the reader can be employed in Stages 1 and 2.

For example, when the symbol rate in the streaming phase is 10 kbps,  $m_s = 2$ , and no coding is introduced, the frequencies of the subcarriers 1, 2, and 3 are 20, 40, and 60 kHz, respectively.

To facilitate the demodulation in the reader, we employ Miller encoding or differential Miller encoding along with subcarrier coding.

Figure 4 Subcarrier frequency and symbol

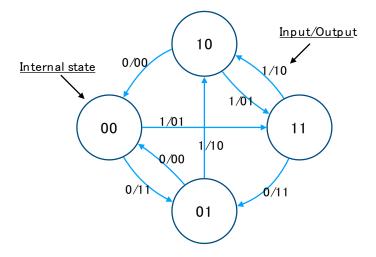

The state diagram of Miller encoding is shown in Figure 5.

Figure 5 Miller coding state transition

The subcarrier is XORed with Miller encoded baseband signal except for the preamble, as explained below.

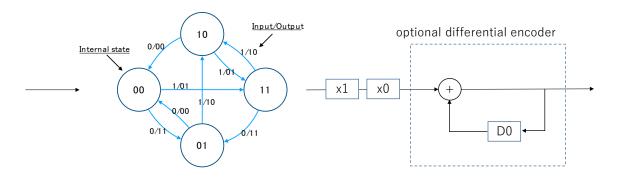

The differential Miller encoding state model and differential encoder are shown in Figure 6.

D0 shall be set to zero at the beginning of each frame

#### Figure 6 Differential Miller coding

## 2.2 Streaming frame

A stream tag comprises a continuous frame, shown in Figure 7, to transfer streaming data to the reader in Stage 3. The leading 5 bits are the preamble without Miller encoding. The rest of the frame should be encoded with Miller or differential Miller coding. Furthermore, the rest of the frame should produce the CRC-16, as follows.

- Generation polynomial is  $x^{16} + x^{12} + x^5 + 1$

- 16 bits register preloaded with 0xFFFF

- · Data MSB was input and all the data clocked

- The final 16 bits inverted to obtain CRC-16

For checking, the register filled with 0xFFFF, all the data including CRC-16 clocked, and checked if the output is 0x1D0F

It should be noted that zone ID is specified by the reader, whereas sequence ID is the frame ID automatically incremented by one in each frame. The data length N is specified by the reader with the STR\_CNT register.

| Preamble            | Zone ID | Sequence ID                   | Data       | CRC16   |

|---------------------|---------|-------------------------------|------------|---------|

| 5 bit<br>equivalent | 3 bits  | 8 bit (0-255 sequential data) | N × 8 bits | 16 bits |

| 1010101010          | 001     | 255                           |            |         |

#### Figure 7 Return link frame structure in stage 3

#### 2.3 Subcarrier allocation and bit rate configuration

Generally, the RFIC design to generate subcarrier frequency in a stream tag falls under the scope of the the manufacturer. However, there is a proven way to generate specified subcarrier frequency with a relatively slow clock rate of the master clock in RFIC is by adjusting the frequency of the oscillator in a tag to be an integer multiple of designated subcarrier frequency; this is done using a digitally controlled ring oscillator (DCRO). Alternatively, subcarrier frequency can be produced by decimating a single master clock. However, in such a design, a high subcarrier frequency tends to involve bias, which may violate the subcarrier accuracy requirement.

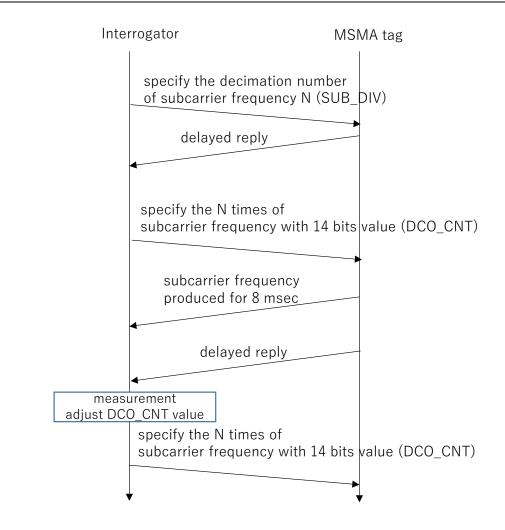

The subcarrier frequency produced by a stream tag does not immediately match the specified frequency owing to the instability of the DCRO clock. Therefore, the proposed communication protocol performs an iterative adjustment wherein two commands, DCO\_CNT and SUB\_DIV, are used repeatedly. The DCO\_CNT command specifies the clock frequency, whereas the SUB\_DIV command specifies the decimation ratio to both produce a subcarrier from the DCRO clock and define the bitrate.

Figure 8 Iterative subcarrier frequency adjustment

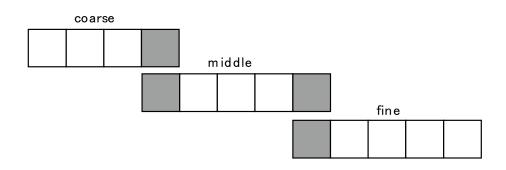

The 14-bit DCRO value comprises overlapped coarse, middle, and find registers (Figure 9).

#### Figure 9 Overlapped DCO\_CNT register value

The 14-bit value X relates to the actual frequency as follows.

$$f = 400 X + 691200$$

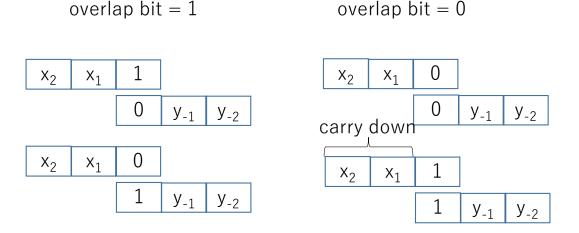

Consequently, one subcarrier frequency can be represented in general with four patterns of register values, thereby allowing some errors in the adjusting accuracy of the DCRO (Figure 10).

#### Figure 10 Candidates to represent one overlap bit

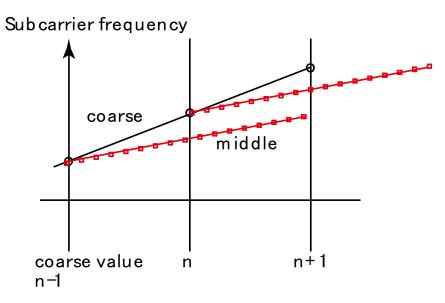

However, the increase in the subcarrier frequency against a unit increase in each register value cannot exceed 2.0 because such a case will produce a gap in the subcarrier frequency that cannot be compensated (Figure 11).

## Figure 11 Slopes of each DCO value cannot be different by more than two times. This figure depicts the cases of coarse and middle registers.

The available subcarrier frequency and bitrate are listed in Table 1. The lowest subcarrier frequency, 100 kHz, is chosen to avoid interference from the powering continuous wave from the reader. The lowest symbol rate is confined to 10 kbps, as lower symbol rate links are affected by DCRO frequency fluctuation.

|    |    |    |         |               | vord  | ¥                     | divid          | der control word           | 1                  | b       | aseband b | it rate (B t | oits ( 6bits | ))      |

|----|----|----|---------|---------------|-------|-----------------------|----------------|----------------------------|--------------------|---------|-----------|--------------|--------------|---------|

| С  | м  | F  | Co<br>C | ode (14b<br>M | r F   | DCO<br>Clock<br>(MHz) | dividing ratio | Dividing ratio<br>(3 bits) | sub. Freq<br>(kHz) | 120kbps | 100kbps   | 40kbps       | 20kbps       | 10kbps  |

| 7  | 29 | 16 | 0111    | 11101         | 10000 | 1.6                   | 16             | 100                        | 100                |         |           |              |              | 0001010 |

| 10 | 31 | 16 | 1010    | 11111         | 10000 | 1.92                  | 16             | 100                        | 120                |         |           |              | 0000110      | 0001100 |

| 3  | 18 | 16 | 0011    | 10010         | 10000 | 1.12                  | 8              | 011                        | 140                |         |           |              |              | 0001110 |

| 4  | 27 | 16 | 0100    | 11011         | 10000 | 1.28                  | 8              | 011                        | 160                |         |           | 0000100      | 0001000      | 0010000 |

| 6  | 20 | 16 | 0110    | 10100         | 10000 | 1.44                  | 8              | 011                        | 180                |         |           |              |              | 0010010 |

| 7  | 29 | 16 | 0111    | 11101         | 10000 | 1.6                   | 8              | 011                        | 200                |         | 0000010   |              | 0001010      | 0010100 |

| 9  | 22 | 16 | 1001    | 10110         | 10000 | 1.76                  | 8              | 011                        | 220                |         |           |              |              | 0010110 |

| 10 | 31 | 16 | 1010    | 11111         | 10000 | 1.92                  | 8              | 011                        | 240                | 0000010 |           | 0000110      | 0001100      | 0011000 |

| 2  | 21 | 24 | 0010    | 10101         | 11000 | 1.04                  | 4              | 010                        | 260                |         |           |              |              | 0011010 |

| 3  | 18 | 16 | 0011    | 10010         | 10000 | 1.12                  | 4              | 010                        | 280                |         |           |              | 0001110      | 0011100 |

| 3  | 30 | 24 | 0011    | 11110         | 11000 | 1.2                   | 4              | 010                        | 300                |         |           |              |              | 0011110 |

| 4  | 27 | 16 | 0100    | 11011         | 10000 | 1.28                  | 4              | 010                        | 320                |         |           | 0001000      | 0010000      | 0100000 |

| 5  | 23 | 24 | 0101    | 10111         | 11000 | 1.36                  | 4              | 010                        | 340                |         |           |              |              | 0100010 |

| 6  | 20 | 16 | 0110    | 10100         | 10000 | 1.44                  | 4              | 010                        | 360                |         |           |              | 0010010      | 0100100 |

| 7  | 16 | 24 | 0111    | 10000         | 11000 | 1.52                  | 4              | 010                        | 380                |         |           |              |              | 0100110 |

| 7  | 29 | 16 | 0111    | 11101         | 10000 | 1.6                   | 4              | 010                        | 400                |         | 0000100   | 0001010      | 0010100      | 0101000 |

| 8  | 25 | 24 | 1000    | 11001         | 11000 | 1.68                  | 4              | 010                        | 420                |         |           |              |              | 0101001 |

| 9  | 22 | 16 | 1001    | 10110         | 10000 | 1.76                  | 4              | 010                        | 440                |         |           |              | 0010110      | 0101100 |

| 10 | 18 | 24 | 1010    | 10010         | 11000 | 1.84                  | 4              | 010                        | 460                |         |           |              |              | 0101110 |

| 10 | 31 | 16 | 1010    | 11111         | 10000 | 1.92                  | 4              | 010                        | 480                | 0000100 |           | 0001100      | 0011000      | 0110000 |

| 11 | 27 | 24 | 1011    | 11011         | 11000 | 2                     | 4              | 010                        | 500                |         |           |              |              | 0110010 |

| 2  | 21 | 24 | 0010    | 10101         | 11000 | 1.04                  | 2              | 001                        | 520                |         |           |              | 0011010      | 0110100 |

| 2  | 27 | 28 | 0010    | 11011         | 11100 | 1.08                  | 2              | 001                        | 540                |         |           |              |              | 0110110 |

| 3  | 18 | 16 | 0011    | 10010         | 10000 | 1.12                  | 2              | 001                        | 560                |         |           | 0001110      | 0011100      | 0111000 |

| 3  | 24 | 20 | 0011    | 11000         | 10100 | 1.16                  | 2              | 001                        | 580                |         |           |              |              | 0111010 |

| 3  | 30 | 24 | 0011    | 11110         | 11000 | 1.2                   | 2              | 001                        | 600                |         | 0000110   |              | 0011110      | 0111100 |

| 4  | 20 | 28 | 0100    | 10100         | 11100 | 1.24                  | 2              | 001                        | 620                |         |           |              |              | 0111110 |

#### Table 1 Subcarrier and bitrate allocation

An example of subcarrier frequency allocation is explained below.

- i. The reader writes to the SUB\_DIV register as 4 division = b100. The bitrate value in the word does not matter in this particular SUB\_DIV.

- ii. The interrogator writes to the DCO\_CNT register with an appropriate frequency value.

- iii. The tag replies with the DCO\_CNT register divided by four subcarrier frequencies for 8 ms.

- iv. The reader samples the information regarding 1/4<sup>th</sup> DCO frequency and issues an updated DCO\_CNT value to compensate for the error.

#### Example:

Assuming that a reader wants to allocate a 200 kHz subcarrier to a stream tag after inventory, the DCRO frequency of the stream tag should be 1.6 MHz according to Table 1.

For DCO control, the interrogator expects to receive a 400 kHz (1/4<sup>th</sup> DCO) subcarrier for 8 ms after issuing a DCO\_CTL.

- The DCO\_CTL is 0111 11101 10000. Suppose that the received subcarrier is 404000 Hz, which is approximately 1 % higher than the designated frequency. Therefore, the interrogator needs to lower the tag's clock by approximately 1 %.

- ii. The interrogator knows that the DCRO frequency is 1.6 MHz and the received subcarrier frequency is multiplied by four. This yields 1616 = 404 × 4 kHz, which is 16 kHz higher than the designated frequency. The DCRO frequency can be adjusted with 0.4 kHz resolution for 1 bit of DCRO fine division (5 bits from LSB (the Least Significant Bit)).

- iii. The bias of 16 kHz can be compensated with 16/0.4 = 40 = 0 × 28 = b0010

1000, which is subtracted from the original DCO\_CNL = 0111 11101 10000.

This yields 0111 11100 01000.

## 2.4 Writing configuration with Gen2 WRITE command

The reader assigns and allocates subcarriers to stream tags and configures their sensors using Gen2 WRITE command. The structure of a WRITE command is shown in Figure 12. WordPtr uses Extensible Bit Vectors defined in Gen2. Special register addresses for subcarrier allocation and sensor configuration are specified.

| Write (8 bit) | Membank             | WordPtr | Data (XORed with<br>handle) | Handle | CRC16   |

|---------------|---------------------|---------|-----------------------------|--------|---------|

| 11000011      | 2 bits<br>(11:user) | (EB∨)   |                             |        | 16 bits |

#### Figure 12 Gen2 WRITE command

The response from a tag to the reader after receiving a WRITE command is as follows. Upon receiving the WRITE command, a tag responds with the following delayed reply. When an MSMA tag fails to perform the instructed write or configure, it replies with Success/Fail = 1 with a proper error code defined in Annex I of [1].

| Preamble        | Header    | Handle/Error code | CRC16   |

|-----------------|-----------|-------------------|---------|

| 10 bits         | 1 bit     | 16 bits           | 16 bits |

| 4M/BLF + 010111 | 0:success | Handle            |         |

| 4M/BLF + 010111 | 1:fail    | Error code        |         |

The special user memory addresses to stream tag configurations are defined in Table 2. The values should be stored as MSB first byte order. The implementation of the special memory address can be RFIC and/or vendor dependent.

#### Memory alias Memory WordPtr Description SPI\_WRITE Writes a byte data to the SPI 80H interface DCO\_CNT 81H Sets the subcarrier frequency SUB\_DIV Sets the division number of tag 82H clock and bitrate of the subcarrier Sets the write and read SPI\_INST 83H instruction words used in the SPI interface STR\_CNT 84H Specifies the leading address and number of bytes for the sensor to read. Zone ID can also be specified with this command DCO\_LCK DCO frequency lock and 85H unlock. DOC unlock state MSMA tags do not produce subcarrier streaming

#### Table 2 Special register assignment

| SPI_CNTL  | To accommodate many types<br>of SPI sensors, the SPI interface<br>is configured through this<br>register         | 87H |

|-----------|------------------------------------------------------------------------------------------------------------------|-----|

| GPIO_CNTL | To trigger the external sensors<br>and devices, the output port<br>can be toggled by writing to<br>this register | 88H |

#### SPI \_WRITE (80 H)

The high byte and low byte are the address and data to be written, respectively. The tag uses a sensor-specific write command specified in the SPI\_INST register (for example 0x0A, in the case of ADXL). Depending on the type of sensor, the configuration of the sensor is obtained through SPI by writing to the SPI\_WRITE register.

| 15  | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-------|----|----|----|----|---|---|------|---|---|---|---|---|---|---|

| Add | lress |    |    |    |    |   |   | Date | a |   |   |   |   |   |   |

#### DCO\_CNT (81 H)

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Х  | Х  | C3 | C2 | C1 | C0 | M4 | М3 | M2 | M1 | MO | F4 | F3 | F2 | F1 | FO |

Explained in subsection 1.4.

#### SUB\_DIV (82 H)

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Х  | Х  | Х  | Х  | Х  | Х  | S2 | S1 | SO | B6 | B5 | B4 | ВЗ | B2 | B1 | BO |

S2, S1, and S0 : Subcarrier divider control words;

bit rate : B0–B6: bitrate divider control words

#### SPI\_INST (83 H)

This word defines the WRITE and READ command bytes for SPI communication. High 8 bits for WRITE and Iow 8 bits for READ sensor and RFIC communication are shown in Figure 7; for ADXL362, they are 0 × 0A and 0 × 0B, respectively.

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|---|---|-------|----|---|---|---|---|---|---|

| 0 × | 0A |    |    |    |    |   |   | 0 × ( | ЭВ |   |   |   |   |   |   |

#### STR\_CNT (84 H)

This word defines the data to be read from the RFIC The high 8 bits (15:8) is the starting address. Bits 7:4 is the number of bytes minus  $1^2$  to be read. For example, if we read 2 bytes of data, the bits 7:4 shall be 1. bit 3 is to select the antenna and bits 2–0 is to select the ZONE ID. For ADXL362 to read XDATA, YDATA, ZDATA, TEMP (total 16 × 4 = 64 bits = 8 bytes).

Additionally, STR\_CNT is used to read the SPI register value by the Gen2 Read command, as explained in the SPI\_READ subsection. Although the SPI register is usually bound by a byte, Gen2 READ always returns two bytes (one word) of data. Therefore, the number of bytes should be an odd number, such as 1, 3, 5, and the second byte should be discarded by the interrogator.

| 15  | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6                        | 5      | 4 | 3   | 2    | 1    | 0 |

|-----|-------|----|----|----|----|---|---|------------|--------------------------|--------|---|-----|------|------|---|

| Ado | dress |    |    |    |    |   |   | # c<br>rea | of by <sup>.</sup><br>Id | tes to | C | RFU | ZONE | E ID |   |

| 0 × | × 08  |    |    |    |    |   |   | 100        | 00                       |        |   | 0   | 001  |      |   |

#### DCO\_LCK (85 H)

To avoid unexpected or accidental streaming from background stream tags, the reader should explicitly report the completion of subcarrier allocation to the stream tags. This completes their subcarrier allocation by writing the or unlock bool value, zone ID, and coding method to the DCO\_LCK register. The default value of the lock flag when a tag wakes up is "unlock". A stream tag does not start streaming even upon receiving the

<sup>&</sup>lt;sup>2</sup> This "minus 1" is to specify up to 16 bytes of data instead of 15 bytes.

STRM\_START command if its lock flag is "unlock" or its zone ID does not match the specified zone ID in STRM\_START.

| 15–10 | 9                 | 8                   | 7                                | 6               | 5   | 4   | 3                 | 2–0 |

|-------|-------------------|---------------------|----------------------------------|-----------------|-----|-----|-------------------|-----|

| RFU   | Target<br>SPI add |                     | coding option <sup>3</sup>       |                 | RFU | RFU | Lock flag<br>Lock | RFU |

| X     | -                 | d on the<br>of RFIC | 1 = Miller<br>3 = Miller differe | ential encoding |     |     | 0:false<br>1:true |     |

Response to writing to the DCO\_LCK register is given as follows.

| Preamble        | Success/Fail | Handle  | CRC16   |

|-----------------|--------------|---------|---------|

| 10 bits         | 1 bit        | 16 bits | 16 bits |

| 4M/BLF + 010111 | 0:success    |         |         |

|                 | 1:Error      |         |         |

#### SPI\_CNTRL(87H)

This word defines the behavior settings of the SPI interface for various sensors. The default value at reset is 0x0000. The register value is given as follows.

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7           | 6           | 5  | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|---|------|-------------|-------------|----|---|---|---|---|---|

| RFU |    |    |    |    |    |   | ASSL | ACC_<br>OFF | spi_<br>mod | E  |   |   |   |   |   |

| 0   | 0  |    |    |    |    |   |      | 0           | 0           | 00 |   |   |   |   |   |

Bit 3: ASSL (active slave select level), which is chip select (CS) status for an active slave device.

<sup>&</sup>lt;sup>3</sup> Coding options 0 and 2 are used for experimental convolutional coding.

0: Active L level, 1: Active H level

Bit 2: ACC\_OFF (Auto Command Code OFF)

0: The command code defined by SPI\_INST is automatically added to the SPI Write/Read sequence.

1: The command code defined by SPI\_INST is NOT automatically added in the SPI Write/Read sequence.

Bit 1, 0: SPI\_MODE, which specifies the operation mode (clock polarity and phase) in SPI communication. CPOL and CPHA should be set by the RFIC to the following values.

| SPI mode | CPOL | СРНА | Data shift timing | Data sampling timing |

|----------|------|------|-------------------|----------------------|

| 00       | 0    | 0    | SCK falling ddge  | SCK rising edge      |

| 01       | 0    | 1    | SCK rising edge   | SCK falling edge     |

| 10       | 1    | 0    | SCK rising edge   | SCK falling edge     |

| 11       | 1    | 1    | SCK falling edge  | SCK rising edge      |

CPOL: clock polarity

CPOL = 0 is a CS that idles at 0

CPOL = 1 is a CS that idles at 1.

CPHA: Clock phase

CPHA determines the timing (i.e. phase) of the data bits relative to the clock pulses.

#### GPIO\_CTRL(88H)

This word sets the external GPIO value as OUTPUT. The number of GPIO ports depends on the available PADS. As a tentative value, the following defines four GPIO ports.

| 15–4 | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|

| RFU  | GPIO 3 | GPIO 2 | GPIO 1 | GPIO 0 |

| 0    | 0      | 0      | 0      | 0      |

- Bit 3: GPIO port 3 High/Low (default pull down)

- Bit 2: GPIO port 2 High/Low (default pull down)

- Bit 1: GPIO port 1 High/Low (default pull down)

Bit 1: GPIO port 0 High/Low (default pull down)

#### DEMO\_CLK(8AH)

This word sets the bitrate of the interrogator-to-tag link for StreamStop.

| 15–8 | 7-0                  |

|------|----------------------|

| RFU  | Division             |

| 0x0A | 0x28 (default value) |

Division: The divisor to produce the subcarrier synchronized decimation to match 10 kbps downlink. The default value is 40 = 0x28, which can only work with 400 kHz subcarrier frequency. If subcarrier frequency is 240 kbps, Divisor shall be 24 = 0x08. This register shall be set before issuing a StreamStart command.

## 2.5 SPI\_READ with Gen2 READ command

SPI registers can be read by a combination of STR\_CTL(84H) and Gen2 READ commands. Before any reading of the SPI register, the register address should be specified by STR\_CTL (84H). The register data are moved to the two bytes buffers 8CH to 8FH (2 bytes × 4 = 4 words = 8 bytes).

A Gen2 Read command for specifying the special address of USER memory 8CH (EVB 1000 0001 0000 1100) is translated as an instruction to read an SPI memory. If the destination sensor is capable of reading up to two words, the LSB should be the data of the specific register. If the sensor is not capable of reading multiple bytes, the second byte is padded with zeros.

| F | READ MEMBANK | WORDPTr | WordCount | RN | CRC |  |

|---|--------------|---------|-----------|----|-----|--|

|---|--------------|---------|-----------|----|-----|--|

| 8        | 2       | EBV (2<br>bytes) | 8                                              | 16 bits | 16     |

|----------|---------|------------------|------------------------------------------------|---------|--------|

| 11000010 | 11:USER | 8CH              | Number of<br>words to<br>read (from<br>1 to 4) | handle  | CRC-16 |

Note that WORDPTr should always be a fixed value. We use 8CH but it can be RFIC manufacture/vendor dependent. It cannot be 8D, 8E, or 8F even when we read multiple words. WordPtr format of 8CH is as follows.

| Second byte |          |   | First byte |  |  |

|-------------|----------|---|------------|--|--|

| 7           | 6–0      | 7 | 6–0        |  |  |

| 1           | 000 0001 | 0 | 000 1100   |  |  |

Tag reply to a successful Read command follows the Gen2 protocol and is given as follows.

| Header | Memory Words | RN      | CRC    |

|--------|--------------|---------|--------|

| 8      | 1 word       | 16 bits | 16     |

| 0      | Data         | handle  | CRC-16 |

## 2.6 Sensor data streaming SPI interface exchange

The RFIC in a stream tag should collect sensor data through the SPI interface and plug the data into the streaming frame. The data obtained from a sensor are synchronously transferred to the backscatter modulator, as shown in Figure 15.

This can be done by providing the bitrate-level CLK signal from the RFIC and sensor. Furthermore, the SPI sensor should have the capability to stream continuously.

|                        |                    |                   |                    |                                                  | •••           |                               | <u></u>  |

|------------------------|--------------------|-------------------|--------------------|--------------------------------------------------|---------------|-------------------------------|----------|

| SCLK                   | ئىرىپ              | ى<br>ئىرىنى       |                    |                                                  |               | mmm                           |          |

| MOSI                   |                    |                   | BIT ADDRESS        |                                                  | ····          |                               |          |

| мıso —<br>SPI interfad | e                  |                   |                    | 7 (6 ) 5 ) 4 ) 3 / 2 ) 1 / 0 )                   | •••           | 7 7 6 7 5 7 4 7 3 7 2 7 1 7 0 | <b>)</b> |

|                        |                    |                   |                    | ldress may be aggregat<br>Fin SPI_CNTRL register |               |                               |          |

|                        | Preamble<br>5 bits | Zone ID<br>3 bits | Sequence<br>8 bits |                                                  | Data<br>N x 8 |                               | CRC-16   |

Backscatter link

#### Figure 13 Sensor data encapsulation in the streaming stage

## 2.7 Start streaming

This command triggers the streaming from the designated interrogation zone, which is specified using the zone ID. The command bits use one of the RFU commands of Gen2, as given below.

| Command (STRM_START) | Zone ID | CRC   |

|----------------------|---------|-------|

| 8                    | 3       | CRC-5 |

| 11011010             | zone ID | CRC-5 |

STRM\_START should be preceded by FrameSync of Gen2. The selection of the embed sensors or the external analog sensor should be specifiedby writing to the DCO\_LCK register. Generally, the streaming start command is issued repeatedly for two or three times to avoid any stream tag from failing to start. Stream tags, whose Zone IDs are different from the Zone ID in a stream start command, continue to remain in the DCO\_LCK state, as shown in Figure 3.

## 2.8 Stream stop

The reader can suspend ongoing streaming from a group of stream tags that belong to a specified Zone ID. Frame\_START and Frame END are demanded for tags to prepare for the demodulation. The technical discussion of full duplex backscatter is provided in [5]

| Frame_START | Command (STRM_STOP) | Zone ID | CRC   | Frame END    |

|-------------|---------------------|---------|-------|--------------|

| 6           | 8                   | 3       | CRC-5 | 4            |

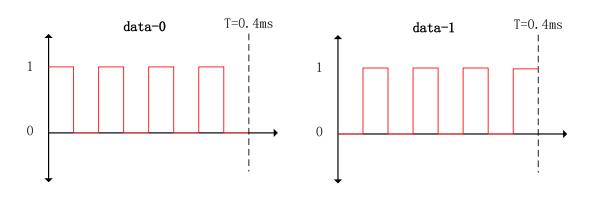

| 101010      | 11011011            | zone ID | CRC-5 | 4 bit data-0 |

The STRM\_STOP command (or the repeated STRM\_STOPs to avoid decoding failure in the backscatter sensor) is special because it is issued by the reader while a group of stream tags backscatter. STRM\_STOP uses the subcarrier coding instead of Miller coding to facilitate the demodulation and timing synchronization in the stream tag.

The reader-to-tag link for STRM\_STOP should employ the following parameters to realize a full duplex while a group of tags is backscattering.

• Low modulation index coded subcarrier: the subcarrier frequency is 10 kHz and forward link bitrate is 2.5 kbps (4 subcarrier cycles per bit). This is to facilitate the demodulation in a stream tag. The subcarrier adoption is to shift the downlink signal from the DC component, which is strongly suppressed by the HPF (High Pass Filter) in a backscatter sensor.

- 0° phase for data 0° and 180° phases for data 1 in the subcarrier.

- Modulation index = 0.1

- Pulse shaped with raised cosine filter with roll-off factor 1.0

STRM\_STOP command shall be preceded with the 16 bits data 0.

## Reference

- "ISO/IEC 18000-63, Information Technology–Radio frequency identification for item management-, Part 63 parameters for air interface communications at 860 MHz to 960 MHz type C," 2015.

- [2]. J. Mitsugi, Y. Kawakita, K. Egawa, and H. Ichikawa, "Perfectly synchronized Streaming from multiple digitally modulated backscatter sensor tags," IEEE Journal of Radio Frequency Identification, vol. 3, no. 3, pp. 149-156, Sept. 2019, doi: 10.1109/JRFID.2019.2914246.

- [3].Nitish Rajoria, Yuki Igarashi, Jin Mitsugi, Yusuke Kawakita, and Haruhisa Ichikawa, "Comparative analysis on channel allocation schemes in multiple subcarrier passive communication system," IEICE TRANSACTIONS on Communications vol. E98-B No.9 pp.1777-1784, (2015). doi: 10.1587/transcom.E98.B.1777.

- [4].Kuanfeng Tang, Chao Zhang, Maodong Wang, Xu. Shengliang, Ji. Shujiang, Na Yan, Hao Min, and Jin Mitsugi. "A novel method to improve the subcarrier frequency accuracy for UHF RFID sensing system," In IEEE RFID 2021 (Virtual Event, USA). pp.1-6, (2021), doi: 10.1109/RFID52461.2021.9444388.

- [5]. J. Mitsugi, Y. Kawakita and H. Ichikawa, "Full duplex backscatter communication with subcarrier synchronized decimation," 2021 IEEE Wireless Communications and Networking Conference (WCNC), 2021, pp. 1-6, doi: 10.1109/WCNC49053.2021.9417289.

## Acknowledgement

This work includes the results of the research and development for expanding radio resources (JPJ000254) conducted in FY2021 by the Ministry of Internal Affairs and Communications.

# A. Guidelines for ADXL362 configuration through Gen2 WRITE commands

## a. Prerequisite

Data streaming from ADXL362 with a stream tag requires the following configuration using Gen2 memory WRITE commands. An example connection between the RFIC and ADXL362 is shown in Figure 15.

|      | MISO  |                    |

|------|-------|--------------------|

|      | MOSI  |                    |

|      | SCLK  |                    |

| RFIC | CS    | SPI Slave (sensor) |

|      | VDD_S |                    |

|      | VDD   |                    |

|      | VSS   |                    |

|      |       |                    |

| PAD name  | category                         | Туре         | Output/Input | Value                   |

|-----------|----------------------------------|--------------|--------------|-------------------------|

| MISO      |                                  | Digital      | Input        | high:1.6~2.5V,<br>low:0 |

| MOSI      | SPI                              | Digital      | Output       | high:1.6~2.5V,<br>low:0 |

| SCLK      | Digital                          |              | Output       | high:1.6~2.5V,<br>low:0 |

| VSS       | Signal GND                       | Power        | Input/Output | 0                       |

| VDD_S     | SPI output voltage<br>regulation | Digital      | Input        |                         |

| VDD       |                                  | Power        | Output       | 1.4V~2V                 |

| Antenna N |                                  | RF antenna N |              |                         |

| Antenna P |                                  | RF antenna P |              |                         |

#### Figure 15 RFIC, ADXL362, and Interrogator interface diagram

Before any GEN2 READ/WRITE command issuance, SPI READ/WRITE commands (which are 0 × 0B and 0 × 0A for ADXL362, respectively) should be registered to RFIC by issuing a WRITE to SPI\_INST (83 H = EBV10000011) of the user memory (bank 11) to obtain the following.

| WRITE    | Membank | WordPtr  | Data        | Handle  | CRC-16  |

|----------|---------|----------|-------------|---------|---------|

| 11000011 | 11      | 10000011 | 16 bits XOR | 16 bits | 16 bits |

|          |         |          | with handle |         |         |

## b. Writing to ADXL register

A Gen2 WRITE command to a specific user memory (address  $0 \times 80 = EBV 1000000$ ) in user memory bank (bank 11) received by the RFIC passes through to the SPI using the registered WRITE command. For example, if we write a byte data point ( $0 \times aa$ ) to a specific address of ADXL ( $0 \times 77$ ), the WRITE command is as follows.

| WRITE    | Membank | WordPtr  | Data                                           | Handle  | CRC-16  |

|----------|---------|----------|------------------------------------------------|---------|---------|

| 11000011 | 11      | 10000000 | 16 bits (0<br>× 77aa)<br>XOR<br>with<br>Handle | 16 bits | 16 bits |

|          |         |          | панаје                                         |         |         |

After receiving the WRITE command, the tag responds with a delayed reply, which comprises a sequence of specified subcarriers of 43 bit duration.

| Preamble        | Success/Fail | Handle  | CRC16   |

|-----------------|--------------|---------|---------|

| 10 bits         | 1 bit        | 16 bits | 16 bits |

| 4M/BLF + 010111 | 0: success   |         |         |

|                 | 1:Error      |         |         |

## c. Popular configuration parameters

The following is the configuration of ADXL applied in our experiments.

| Description | SPI address | Data example | Note |

|-------------|-------------|--------------|------|

|-------------|-------------|--------------|------|

| 0 × 20 | 0 × 96                                         | Data are the direct reading of the                                                                                                                                                                                                                          |

|--------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                | acceleration level that activates the                                                                                                                                                                                                                       |

|        |                                                | MEMS sensor. 0 × 96 = 150 mg                                                                                                                                                                                                                                |

|        |                                                | activation.                                                                                                                                                                                                                                                 |

|        |                                                |                                                                                                                                                                                                                                                             |

| 0 × 21 | 0 × 00                                         | The threshold level can be specified                                                                                                                                                                                                                        |

|        |                                                | with 11 bit data.                                                                                                                                                                                                                                           |

|        |                                                |                                                                                                                                                                                                                                                             |

| 0 × 22 | 0 × 01                                         | To avoid false triggering, several                                                                                                                                                                                                                          |

|        |                                                | samples are used to distinguish                                                                                                                                                                                                                             |

|        |                                                | between the activate and inactivate                                                                                                                                                                                                                         |

|        |                                                | functions. The absolute time is                                                                                                                                                                                                                             |

|        |                                                | determined by DATA/output data                                                                                                                                                                                                                              |

|        |                                                | rate (ODR). ODR is defined in Filter                                                                                                                                                                                                                        |

|        |                                                |                                                                                                                                                                                                                                                             |

|        |                                                | Control (0 × 2C) register.                                                                                                                                                                                                                                  |

| 0 × 27 | 0 × 01                                         | Activity Enabled = $0 \times 01$ , otherwise 0                                                                                                                                                                                                              |

|        |                                                | × 00, activity is not detected. The                                                                                                                                                                                                                         |

|        |                                                | sensor is always on and consumes                                                                                                                                                                                                                            |

|        |                                                | power. Engaging inactivity by                                                                                                                                                                                                                               |

|        |                                                | defining an inactive threshold level                                                                                                                                                                                                                        |

|        |                                                | can be a viable option.                                                                                                                                                                                                                                     |

| 0 07   | 000                                            |                                                                                                                                                                                                                                                             |

| 0 × 2/ | 0 × 00                                         | FIFO disabled. The sensor data are                                                                                                                                                                                                                          |

|        |                                                | retrieved by RFIC and streamed to the                                                                                                                                                                                                                       |

|        |                                                | interrogator by consecutively issuing                                                                                                                                                                                                                       |

|        |                                                | SPI_READ (0 × 0B) command by RFIC.                                                                                                                                                                                                                          |

| 0 × 2C | 0 × 45                                         | The acceleration range and ODR.                                                                                                                                                                                                                             |

|        |                                                | 0 × 05 = max 2 g and 200 Hz                                                                                                                                                                                                                                 |

|        |                                                | 0 × 45 = max 4 g and 400 Hz                                                                                                                                                                                                                                 |

| 0 × 2D | 0 × 02                                         | 0 × 00: standby (low power                                                                                                                                                                                                                                  |

|        |                                                | consumption: 10 nA)                                                                                                                                                                                                                                         |

|        |                                                |                                                                                                                                                                                                                                                             |

|        | 0 × 21<br>0 × 22<br>0 × 27<br>0 × 27<br>0 × 27 | $0 \times 21$ $0 \times 00$ $0 \times 22$ $0 \times 01$ $0 \times 27$ $0 \times 01$ $0 \times 27$ $0 \times 01$ $0 \times 27$ $0 \times 00$ |

The streaming data length and Zone ID can be configured by writing the following one word data.

| 15               | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7     | 6    | 5  | 4   | 3   | 2    | 1 | 0 |

|------------------|----|----|----|----|----|---|-----|-------|------|----|-----|-----|------|---|---|

| Starting address |    |    |    |    |    |   | # 0 | of by | ytes | to | RFU | Zon | e ID |   |   |

|                  |    |    |    |    |    |   |     | rea   | bd   |    |     |     |      |   |   |

The addresses to retrieve data (12-bit data LSB) are as follows:

| 0x0E | XDATA_L | [7:0] |

|------|---------|-------|

| 0x0F | XDATA_H | [7:0] |

| 0x10 | YDATA_L | [7:0] |

| 0x11 | YDATA_H | [7:0] |

| 0x12 | ZDATA_L | [7:0] |

| 0x13 | ZDATA_H | [7:0] |

| 0x14 | TEMP_L  | [7:0] |

| 0x15 | TEMP_H  | [7:0] |

|      |         |       |

The example data to read XDATA, YDATA, ZDATA, TEMP (total  $16 \times 4 = 64$  bits = 8 bytes), and Zone ID = 1 are as follows.

| 1 | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7  | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|---|--------|----|----|----|----|----|---|-----|----|---|---|---|-----|---|---|---|

| С | 0 × 0E |    |    |    |    |    |   | 100 | 00 |   |   |   | 001 |   |   |   |

This 16 bit value (0  $\times$  0e81) should be written to STR\_CNT (0  $\times$  85) in the user memory bank with a WRITE command such that

| WRITE    | Membank | WordPtr  | Data                                           | Handle  | CRC-16  |

|----------|---------|----------|------------------------------------------------|---------|---------|

| 11000011 | 11      | 10000101 | 16 bits (0<br>× 0e81)<br>XOR<br>with<br>Handle | 16 bits | 16 bits |

| D. Kevision n  |         |                                     |

|----------------|---------|-------------------------------------|

| Date           | Version | Note                                |

| June 15, 2021  | 1.0     | Initial version                     |

| July 1, 2021   | 1.1     | Editorial and format change         |

| July 7, 2021   | 1.2     | Editorial change                    |

| April 15, 2022 | 2.0     | Revision of Jupiter 2 RFIC          |

| April 21, 2022 | 2.0.1   | SPR can be vendor dependent.        |

| May 7, 2022    | 2.0.2   | After thorough proofread            |

| May 8, 2023    | 2.1     | Reflecting Jupiter 2 prototype test |

## **B. Revision History**